- Home

- About Us

- Students

- Academics

-

Faculty

- Electrical Engineering

- Automation

- Computer Science & Engineering

- Electronic Engineering

- Instrument Science and Engineering

- Micro-Nano Electronics

- School of Software

- Academy of Information Technology and Electrical Engineering

- School of Cyber Security

- Electrical and Electronic Experimental Teaching Center

- Center for Advanced Electronic Materials and Devices

- Cooperative Medianet Innovation Center

- Alumni

-

Positions

-

Forum

News

- · Shanghai Jiao Tong University professors Lian Yong and Wang Guoxing's team have made remarkable progress in the field of high-efficiency pulse neural network accelerator chips.

- · AI + Urban Science research by AI Institute was selected as cover story in Nature Computational Science!

- · The first time in Asia! IPADS's Microkernel Operating System Research Wins the Best Paper Award at SOSP 2023

- · Delegation from the Institution of Engineering and Technology Visits the School of Electronic Information and Electrical Engineering for Journal Collaboration

- · Associate professor Liangjun Lu and research fellow Jiangbing Du from Shanghai Jiao Tong University made important advancements on large capacity and low power consumption data transmission

Shanghai Jiao Tong University professors Lian Yong and Wang Guoxing's team have made remarkable progress in the field of high-efficiency pulse neural network accelerator chips.

Recently, the Bio-Circuits and Systems Laboratory, led by Professors Lian Yong and Wang Guoxing from the Department of Micro-Nano Electronics (School of Integrated Circuits) at the School of Electronic Information and Electrical Engineering, has made significant progress in the field of high-efficiency pulse neural network accelerator chips. The related results were published under the title "A 0.67-to-5.4 TSOPs/W Spiking Neural Network Accelerator With 128/256 Reconfigurable Neurons and Asynchronous Fully Connected Synapses" in the internationally renowned journal, IEEE Journal of Solid-State Circuits (JSSC).

The first author of the paper is Qi Xiang'ao, a doctoral student in the Department of Micro-Nano Electronics at the School of Electronic Information and Electrical Engineering, and the corresponding author is his advisor, Associate Professor Zhao Jian.

Paper link: https://ieeexplore.ieee.org/document/10546323

Research Methodology:

Spiking Neural Network (SNN) accelerators have garnered widespread attention due to their high computational efficiency. However, the varying requirements for neuron models across different use cases and the uneven spike distribution resulting from event-driven operations complicate the optimization of throughput and area for SNN chips, thereby limiting the improvement of chip efficiency.

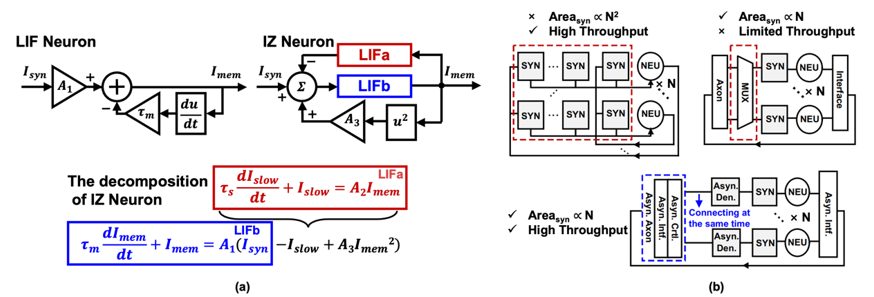

Figure 1. Two innovative technologies in the Spiking Neural Network Accelerator Chip: (a) Reconfigurable Neuron Technology (b) Asynchronous Fully-Connected Synapse Technology

To address the aforementioned issues, the research team developed an SNN chip with 128/256 reconfigurable neurons and asynchronous fully-connected synapses. On one hand, the reconfigurable neuron technology allows the artificial neuron circuits to switch seamlessly between the LIF model and the IZ model according to actual application needs, thereby extending the efficiency advantages of the accelerator to more application scenarios (Figure 1a). On the other hand, the subthreshold asynchronous fully-connected synapses (Figure 1b) provide parallel full connectivity for all neurons on the chip, similar to the human brain, breaking through the bottlenecks of energy consumption and unit throughput rate of SNN accelerators. The overall architecture of the chip is shown in Figure 2a.

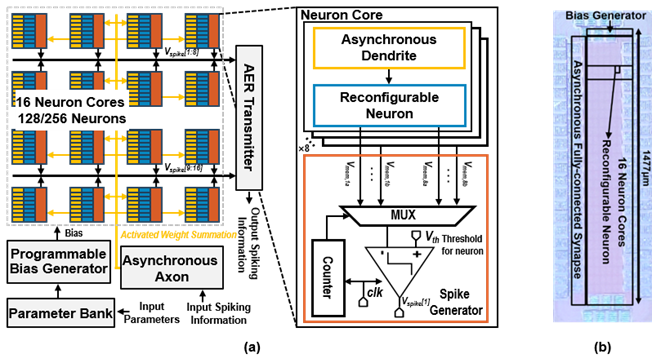

Figure 2. System block diagram and micrograph of the Spiking Neural Network (SNN) accelerator chip.

Results and Impact:

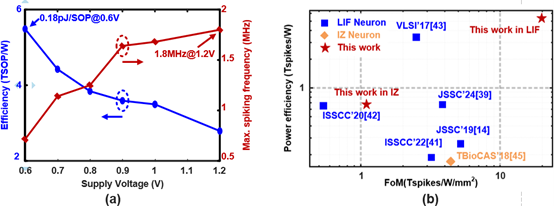

The research team developed the chip prototype using a 55-nm CMOS process (Figure 2b). The proposed chip achieved a peak power efficiency of 5.37 TSOPs/W and a throughput of 25.6 MSOPs/s. The combination of near-threshold neuron operation and asynchronous fully-connected synapses resulted in a 9.42-fold reduction in energy efficiency for image feature extraction applications compared to existing works. The chip also demonstrated its efficiency in various applications, including image compression encoding and the simulation of biological neuron characteristics.

Figure 3. Performance metrics of the chip obtained from testing, including energy efficiency and area efficiency.

This study introduces two technologies—lossless neuron reconfiguration and parallel fully-connected neurons—that advance SNN chips in more accurately simulating biological neurons and more efficiently supporting large-scale integration. These innovations pave the way for future applications in biological neural network simulation and high-efficiency brain-like reasoning, providing hardware support for both "studying the brain" and "utilizing the brain" endeavors.

About IEEE JSSC:

The IEEE Journal of Solid-State Circuits (JSSC), as an international flagship journal, aims to publish the latest technological advancements and record-breaking achievements in the field, representing the highest technical standards in academia and industry.

In recent years, the Department of Micro-Nano Electronics at the School of Electronic Information and Electrical Engineering, Shanghai Jiao Tong University, has been dedicated to exploring cutting-edge chip design technologies. They have made breakthroughs in various areas, including on-chip network chips, low-power analog-digital interface circuits, and high-efficiency specialized accelerators. Their findings have been successively published in JSSC.

-

Students

-

Faculty/Staff

-

Alumni

-

Vistors

-

Quick Links